VP9 Video Encoding/Decoding Support On A PC

Introduction

Video decoding/encoding can take place in the

following four types of silicon:

1. General purpose CPU silicon (x86, ARM, SSE, AVX, …)

2. Dedicated CPU silicon (Intel QuickSync, AMD VideoCoreNext)

3. General

purpose GPU silicon (cores) (GPGPU, Cuda, OpenCL, Shaders, …)

4. Dedicated GPU silicon (NVidia PureVideo (decode), NVida NVENC (encode))

4. Dedicated GPU silicon (NVidia PureVideo (decode), NVida NVENC (encode))

(Table 1)

When video is encoded or decoded any combination of the above silicon can be used.

Being this paper is focused on everyday PCs,

I’ve left out things like FPGAs, but you could consider an FPGA solution to be

more like a general purpose GPU silicon solution.

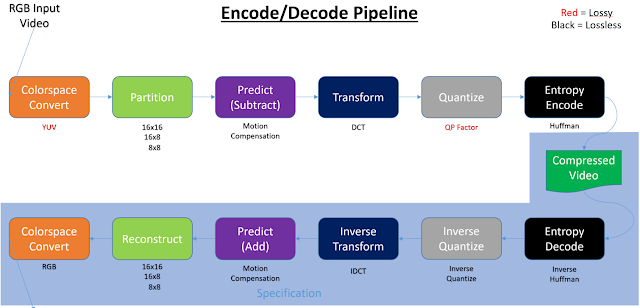

Encoding and decoding of video has a defined

pipeline:

When encoding or decoding video, any one of

those colored blocks can be done in hardware or software. Sometimes a full software approach is taken,

sometimes a full hardware approach is taken, and sometimes any combination of

hardware and software is taken (a hybrid approach) as you progress through the

pipeline.

Video Decoding

To decode a video stream, the person

implementing the decoder can choose different combinations of silicon to use

for each of the colored blocks in the diagram.

Here are some sample combinations, not an exhaustive list:

- Elementary

stream parsing and entropy decode done on the general purpose CPU, with

the rest of the video decode done by GPGPU code.

- Elementary

stream parsing and entropy decode done on the general purpose CPU, with

the rest of the video decode done by dedicated SIP silicon.

- The entire

video stream decoded in dedicated SIP silicon.

Now days, most vendors provide an SIP which

carries out the entire video encode and decode pipeline, so most of the time #3

above is the common use case. But be

aware that the hybrid approach (any mix of the four silicon types mentioned in

Table 1) exists.

VP9 Support on PC’s

The NVidia API that carries out video decoding

is called NVDEC.

NVDEC can offload video decoding to full fixed-function decoding

hardware (Nvidia PureVideo), or (partially) decode via CUDA

software running on the GPU, if fixed-function hardware is not available.

The NVidia API that carries out video encoding

is called NVENC.

The NVENC API is the only way to access the NVidia NVENC SIP core.

AMD

AMD

Video

Core Next is AMDs latest version of its SIP video encoding and

decoding core and it exists on the processor’s die or on an AMD GPU. It replaces the Video Coding Engine that was introduced in

2011, which replaced the Unified Video Decoder.

To understand Video Core Next and the earlier Video Coding Engine, see this article. Note that the article mentions fully fixed encoding (all dedicated silicon) and hybrid encoding (dedicated silicon and OpenCL). These types of approaches are mentioned in Table 1.

To understand Video Core Next and the earlier Video Coding Engine, see this article. Note that the article mentions fully fixed encoding (all dedicated silicon) and hybrid encoding (dedicated silicon and OpenCL). These types of approaches are mentioned in Table 1.

Intel

Intel Quick Sync Video is Intel’s version of

its SIP video encoding and decoding core and it exists on the processor’s die,

it is not a separate GPU.

VP9 Testing Matrix

NVidia (PureVideo), seems to have VP9 support as of

PureVideo’s seventh generation (VP7), starting with the GeForce GTX 960 and

950. This generation of PureVideo HD

corresponds to Nvidia Feature Set F (or "VDPAU Feature Set F").

Here is my usual go to page to figure out

NVidia HW encode and decode support.

AMD (Video Core Next), seems to have added VP9

decode in its Raven Ridge APU (SIP), which dates from January 2018. I would expect AMD’s previous engine, the Video Coding Engine, to have VP9 hardware

support, but I can’t find any supporting information.

Note: AMD marketing coined the term APU, which is a CPU and GPU on a single

die. Intel CPUs also integrate GPU

components onto a single die, but Intel calls this a CPU with integrated

graphics. Yay marketing...

AMD provides APUs and GPUs. Both of these products have built-in VP9 decoding silicon. I don’t see AMD APUs listed in this document. The Raven Ridge APU design exists in the Ryzen 3 2200GE APU and above.

AMD provides APUs and GPUs. Both of these products have built-in VP9 decoding silicon. I don’t see AMD APUs listed in this document. The Raven Ridge APU design exists in the Ryzen 3 2200GE APU and above.

Intel (QuickSync), seems to have added partial VP9

decode as of Version 5 (Skylake), full VP9 decode started with Version 6 (Kaby

Lake) in 2016.

Comments

Post a Comment